J-CPU64 - FPGA based replacement for MOS 6510/8500

FPGA 6510/8500 - J-CPU

FPGA based replacement for MOS 6510 CPU

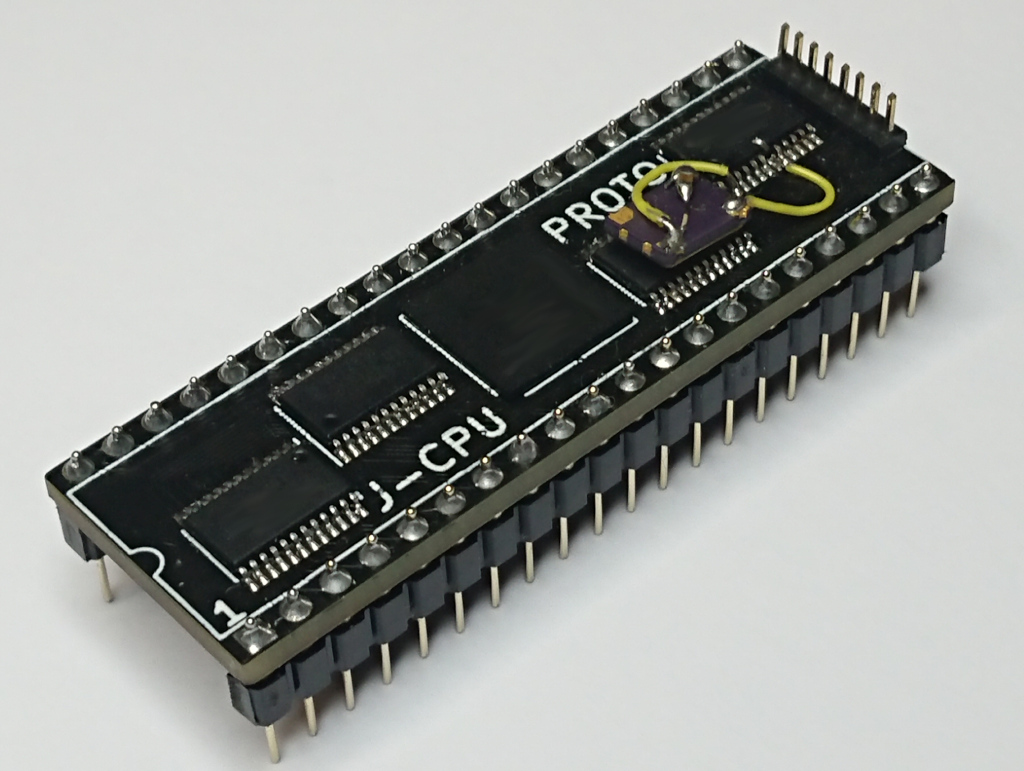

Project started in 2020 by designing PCB. No PCB was populated until summer 2022, when the project continued.

Project goal is to make 100% compatible FPGA replacement for MOS 6510, that is physically same size as original

One goal is to learn more about FPGA designing, so all the code is completely self written

October 2022 status:

About 80% complete. Already usable, with some issues with some games and demos

PCB needs some modifications

All standard instructions implemented

Cycle count not correct with all instructions

Decimal mode not implemented

Only some illegal instructions implemented so far

IRQ interrupts ok, NMI not implemented yet

RDY/AEC logic done and working. HALT timing needs to be checked

Bus timing needs to be checked and adjusted.

January 2023 status:

Decimal mode implemented

All except some unstable illegal instructions implemented

NMI implemented

Still not correct cycle count with all instructions

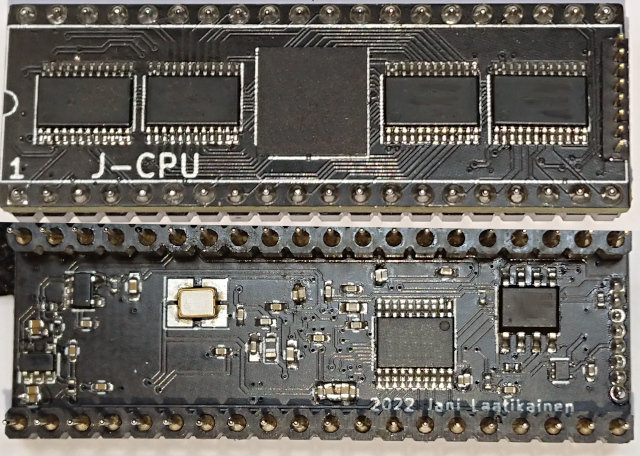

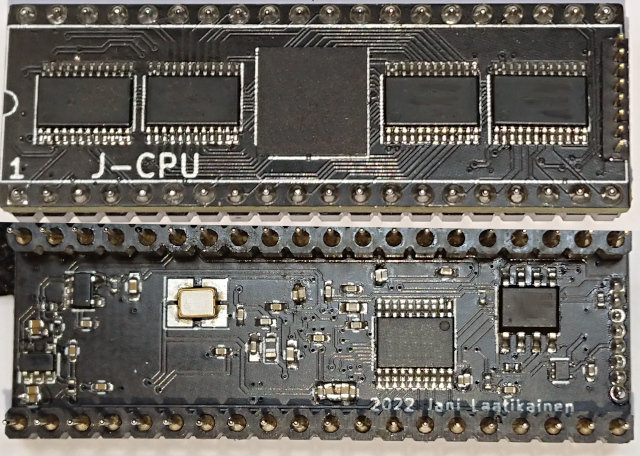

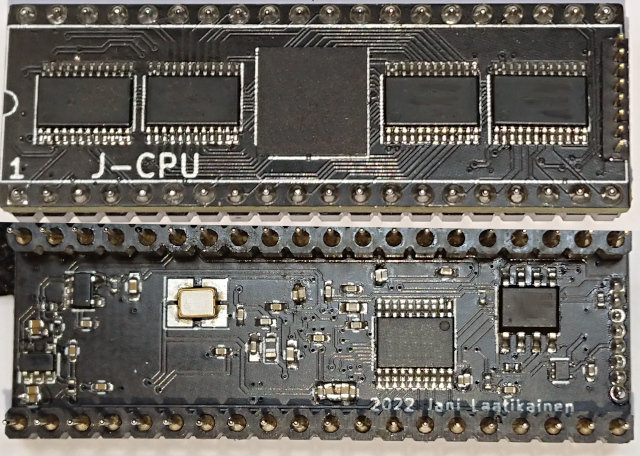

New PCB:

February 2023 status:

Very many bugs fixed

Cycle count is now correct with all instructions, except 2 unimplemented illegal & unstable instructions

Even many demanding PAL-demos work now

Even though mostly works correctly, there is some problems with IRQ, NMI & RDY signal handling, especially when they are overlapping

Some problems with decimal mode, especially with flags when decimal mode is active

April 2023 status:

Once again many bugs fixed

Cycle exact with every instruction now.

All illegal, including the "unstable" instructions implemented. "unstable" functionality needs some checking and possibly fixes

Decimal mode works correctly with all instructions, including illegal instructions

Still some problems with interrupts & rdy

Small problems with phi2 clock signal output

New PCB drawn & ordered, hopefully fixes some small stability issues and phi2 output

November 2023 status:

Every instruction ok now

No stability issues anymore

All relevant Vice-project's test programs and Lorenz's test suite programs passed

Circuit and PCB still needs some small fixes

January 2024 status:

Final testing is underway

Production starting soon

May 2024 status:

J-CPU64 is finally released!

You can buy J-CPU64 at:

Run Stop Re-Store (ships internationally): https://retro8bitshop.com/product/j-cpu64-6510-8500-replacement-for-the-commodore-64/

Retrospective shop (ships internationally): https://retrospective.shop/j-cpu64/

Am-Mek Oy (ships only to Finland): https://shop.am-mek.fi/product/j-cpu64/

Check out also: J-CIA / J-VIC / VIDS

Back to index

2020-2025 Jani Laatikainen

2020-2025 Jani Laatikainen